# **MM5620**

# 64 Gbps High-Speed Differential Loopback Switch (AC coupled)

# **Product Overview**

## **Description**

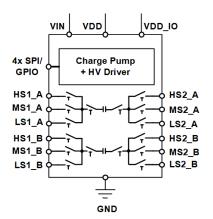

The MM5620 is a high-speed differential loopback switch (AC coupled) supporting the high-speed differential signal switching required in the latest PCIe Gen 5, Gen 6, SerDes, and other standards. The MM5620 is based on Menlo Micro's Ideal Switch® technology and can operate at 64 Gbps with a bandwidth of 20 GHz for high-performance applications. The MM5620 has low insertion loss, fast switching speed, and can operate with greater than 3 billion switching cycles. The MM5620 system-in-package (SiP) solution fully integrates the switch driver and charge pump controlled through SPI or GPIO interfaces by a host processor. In addition, integrated loopback capacitors provide significant board footprint reduction for high-volume production test solutions. The MM5620 switch provides high data rate for full high-speed differential data applications with unprecedented levels of parallel testing for space-constrained final test and probe test. Applications include chip testing for smartphones, graphics, and network processors, as well as microprocessor, accelerator, and high-speed memory products.

## **Features**

- DC to 20 GHz range

- Differential Dual DP3T switch with Loopback

- Normally Open, Reflective actuator

- Low Insertion Loss: -1.5 dB @ 16 GHz

- Integrated charge pump and driver eliminates the requirement for external biasing and driver circuitry

- Built-in AC Coupling Capacitors

- Fully controllable ports for low, medium, and high data rate signal routing

- High Reliability: Greater than 3 billion switching operations

- 8.2 x 8.2 mm LGA Package

#### **Markets**

- Automated Test Equipment

- Measurement Equipment

- Semiconductor Final Package Test

- Compliance and Loopback Test

# **Applications**

- High-Speed Data Digital Component Testing

- Optical-Electrical Module Testing

- High-Speed Signal Routing

- ATE Device Interface Boards

- Optical-Electrical Module Testing

- Differential Switch Matrices

1 © 2024 Menlo Microsystems, Inc. All Rights Reserved

October 29, 2024

www.MenIoMicro.com

# **Electrical Specifications**

## **Operating Characteristics**

#### **Absolute Maximum Ratings**

Exceeding the maximum ratings as listed in <u>Table 1</u> below may reduce the reliability of the device or cause permanent damage. Operation of the MM5620 should be restricted to the limits indicated in the recommended operating conditions listed in <u>Table 2</u>.

#### **Electrostatic Discharge (ESD) Safeguards**

The MM5620 is a Class 0 ESD device. When handling the MM5620, observe precautions as with any other ESD sensitive device. Do not exceed the voltage ratings specified in <u>Table 1</u>.

| Parameter                                        | Symbol                     | Minimum | Maximum                  | Unit |

|--------------------------------------------------|----------------------------|---------|--------------------------|------|

| DC Supply Voltage                                | Vdd                        | -0.3    | 3.6                      | V    |

| I/O Supply Voltage                               | $V_{\text{DD}\_\text{IO}}$ | -0.3    | 5.5                      | V    |

| Charge Pump Input                                | VIN                        | -0.3    | 5.5                      | V    |

| Driver Logic Input Levels                        |                            | -0.3    | V <sub>DD_IO</sub> + 0.3 | V    |

| Max Input Voltage Level (RF Pins) <sup>4,8</sup> |                            | —       | 3.3                      | V    |

| Hot Switching Voltage @ 0.5 V <sup>1, 2</sup>    |                            | -0.5    | 0.5                      | V    |

| Storage Temperature Range <sup>3</sup>           |                            | -65     | 150                      | ٥C   |

| ESD Rating HBM RF Pins <sup>4</sup>              |                            | —       | 150                      | V    |

| ESD Rating HBM Control and Power Pins⁵           |                            | —       | 2000                     | V    |

| ESD Rating HBM VPP Pin                           |                            |         | 500                      | V    |

| Mechanical Shock <sup>6</sup>                    |                            |         | 500                      | G    |

| Vibration <sup>7</sup>                           |                            |         | 500                      | Hz   |

#### **Table 1. Absolute Maximum Ratings**

#### Notes:

1. For hot-switching, differential voltage across switch terminals must be less than or equal to 0.5 V and each switch port must be within +/-0.5 V of RF ground. See section <u>Hot Switch Restrictions</u>.

2. RF pins must not be allowed to electrically float during switch operation. See section <u>Floating Node Restrictions</u> for details on avoiding floating nodes.

- 3. See section Storage and Shelf Life more information on shelf and floor life.

- 4. RF pins include: HS1\_x, HS2\_x, MS1\_x, MS2\_x, LS1\_x, LS2\_x.

- 5. Control and power pins include: VIN, VDD, VDD\_IO, PULL\_UP, FLT\_MODE, FLTB, FLIP\_BIT, SCK/CTL1, MOSI/CTL2, MISO/CTL3, SSB/CTL4, CP\_EN.

- 6. See JESD22-B104 for mechanical shock test methodology at 1.0 ms, half-sine, 5 shocks/axis, 6 axis.

- 7. See JESD22-B103 for vibration test methodology at 3.1 G and 30min/cycle, 1 cycle/axis, 3 axis.

- 8. Maximum RF input power is 20dBm into 50 ohms.

#### **Table 2. Recommended Operating Conditions**

| Parameter                      | Symbol                     | Minimum | Maximum | Unit | Conditions |

|--------------------------------|----------------------------|---------|---------|------|------------|

| Charge Pump Power Supply       | VIN                        | 4.75    | 5.5     | V    |            |

| Driver Logic Supply Voltage    | V <sub>DD</sub>            | 3.0     | 3.6     | V    |            |

| Logic Reference Level (VDD_IO) | $V_{\text{DD}\_\text{IO}}$ | 1.71    | 5.25    | V    |            |

| Operating Temperature          | TA                         | -40     | 85      | °C   | Ambient    |

| Switch Cycle Frequency         |                            |         | 100     | Hz   |            |

## **Electrical Characteristics**

All specifications valid over full supply voltage and operating temperature range unless otherwise noted. Operating with all analog and digital GND pins connected to system ground (0 V).

| Parameter                      | Symbol            | Minimum | Typical | Maximum | Unit | Conditions                 |

|--------------------------------|-------------------|---------|---------|---------|------|----------------------------|

| Operating<br>Frequency Range   |                   | DC      | —       | 20      | dB   |                            |

| Differential<br>Insertion Loss |                   |         |         |         |      |                            |

| HS1 to HS2                     |                   | _       | 1.5     | —       | dB   | @ 16GHz,<br>De-Embedded    |

| MS1 to MS2                     |                   | —       | 2.0     | _       | dB   | @ 16GHz,<br>De-Embedded    |

| LS1 to LS2                     | SDD <sub>21</sub> | _       | 3.0     | —       | dB   | @ 3GHz, Not<br>De-Embedded |

| HS1 to MS1                     |                   | _       | 1.4     | _       | dB   | @ 16GHz,                   |

| HS2 to MS2                     |                   | _       | 1.4     |         | dB   | De-Embedded                |

| HS1 to LS1                     |                   | —       | 2.9     |         | dB   |                            |

| HS2 to LS2                     |                   | _       | 2.9     | —       | dB   | @ 6 GHz, Not               |

| MS1 to LS1                     |                   | —       | 3.1     | —       | dB   | De-Embedded                |

| MS2 to LS2                     |                   | —       | 3.1     | —       | dB   |                            |

| Differential Return<br>Loss    |                   |         |         |         |      |                            |

| HS1 to HS2                     |                   | _       | 28      | —       | dB   | @ 16GHz,<br>De-Embedded    |

| MS1 to MS2                     |                   | —       | 23      | —       | dB   | @ 16GHz,<br>De-Embedded    |

| LS1 to LS2                     | SDD11             | _       | 27      | —       | dB   | @ 3GHz, Not<br>De-Embedded |

| HS1 to MS1                     | 30011             | —       | 13      | —       | dB   | @ 16 GHz, Not              |

| HS2 to MS2                     |                   | —       | 12      | —       | dB   | De-Embedded                |

| HS1 to LS1                     | 1                 | _       | 23      | _       | dB   |                            |

| HS2 to LS2                     |                   | _       | 23      | —       | dB   | @ 6 GHz, Not               |

| MS1 to LS1                     |                   | _       | 25      | _       | dB   | De-Embedded                |

| MS2 to LS2                     |                   | _       | 25      | _       | dB   |                            |

#### **Table 3. RF Performance Specifications**

4

www.MenIoMicro.com

| Parameter              | Symbol            | Minimum | Typical | Maximum | Unit | Conditions                 |

|------------------------|-------------------|---------|---------|---------|------|----------------------------|

| Differential Isolation |                   |         |         |         |      |                            |

| HS1 to HS2             |                   | —       | 67      | —       | dB   | @ 16GHz,<br>De-Embedded    |

| MS1 to MS2             |                   | —       | 47      | —       | dB   | @ 16GHz,<br>De-Embedded    |

| LS1 to LS2             |                   | —       | 56      | _       | dB   | @ 3GHz, Not<br>De-Embedded |

| HS1 to MS1             | SDD <sub>12</sub> | —       | 41      | _       | dB   | @ 16GHz,                   |

| HS2 to MS2             |                   | —       | 40      | —       | dB   | De-Embedded                |

| HS1 to LS1             |                   | —       | 49      | _       | dB   |                            |

| HS2 to LS2             |                   | —       | 49      | —       | dB   | @ 6 GHz, Not               |

| MS1 to LS1             |                   | —       | 50      | —       | dB   | De-Embedded                |

| MS2 to LS2             |                   | _       | 50      | _       | dB   | _                          |

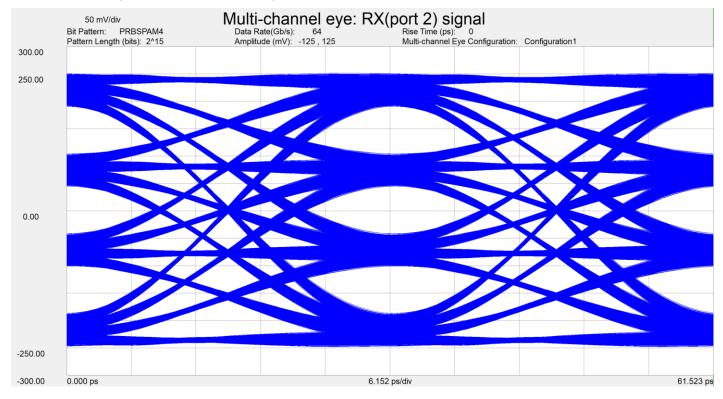

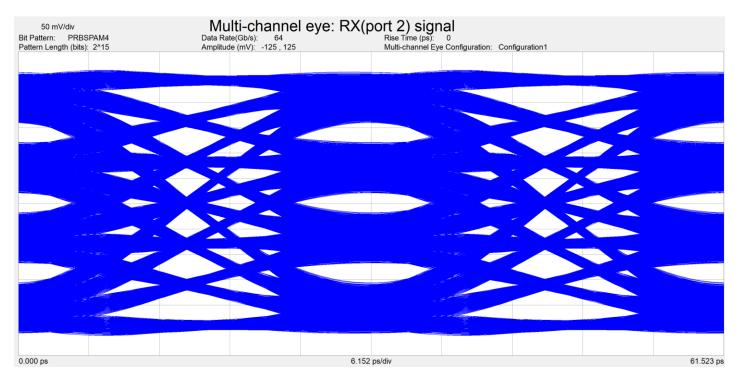

## **Signal Integrity Differential Performance**

Test conditions for the differential PAM4 eye-diagram performance measurements are listed below:

- Analyzed with Physical Layer Test System (PLTS) 2023

- Peak to peak input amplitude: 500 mVpp

- Measurements performed at 64 Gbps

- Signal path: (Figure 1) HS1 to HS2, (Figure 2) MS1 to MS2

- Tests performed at ambient temperature

Figure 1. HS1-HS2 Differential PAM4 Eye Diagram

#### Table 4. HS1-HS2 Differential PAM4 Eye-Diagram Performance

| Еуе | Bit Rate<br>(Gbps) | Eye Height<br>(mV) | Eye Width<br>(ps) | Total Jitter<br>(RMS, ps) |

|-----|--------------------|--------------------|-------------------|---------------------------|

| 0/1 | 64                 | 83.6               | 11                | 10.2                      |

| 1/2 | 64                 | 84.2               | 13                | 8.5                       |

| 2/3 | 64                 | 84.2               | 11                | 10.4                      |

6 © 2024 Menlo Microsystems, Inc.

All Rights Reserved

rved October 29, 2024

www.MenIoMicro.com

Figure 2. MS1-MS2 Differential PAM4 Eye Diagram

| Еуе | Bit Rate<br>(Gbps) | Eye Height<br>(mV) | Eye Width<br>(ps) | Total Jitter<br>(RMS, ps) |

|-----|--------------------|--------------------|-------------------|---------------------------|

| 0/1 | 64                 | 35.8               | 7                 | 15.65                     |

| 1/2 | 64                 | 35.9               | 9                 | 17.34                     |

| 2/3 | 64                 | 36.0               | 7                 | 16.45                     |

## Table 5. MS1-MS2 Differential PAM4 Eye-Diagram Performance

| Parameter                                                     | Symbol | Minimum           | Typical   | Maximum | Unit     | Conditions                          |

|---------------------------------------------------------------|--------|-------------------|-----------|---------|----------|-------------------------------------|

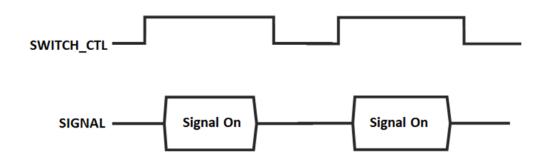

| On / Off Switching<br>Settling time: on<br>Settling time: off |        |                   | 26.5<br>9 | _       | hs<br>hs | Includes settling time.             |

| On / Off Switch<br>Operations <sup>2</sup>                    |        | 3x10 <sup>9</sup> | —         | —       | Cycles   | Specified at 25°C ambient.          |

| Off-State Leakage<br>Current at 30V <sub>DC</sub>             |        | _                 | 7         | 60      | nA       |                                     |

| On-State Resistance <sup>3</sup>                              | Ron    | —                 | 1.7       | 4.0     | Ω        | Specified for all DC-coupled paths. |

#### Table 6. Switch DC and AC Electrical Characteristics<sup>1</sup>

#### Notes:

1. DC measurements were performed in single-ended configuration.

2. Predicted number of operation cycles as observed on a sample size of 75 units, 100Hz cycle rate, and room temperature with Hot Switch Restrictions.

3. Measured at 30mA, DC.

| Parameter                                    | Symbol              | Minimum | Typical | Maximum | Unit | Conditions                                            |

|----------------------------------------------|---------------------|---------|---------|---------|------|-------------------------------------------------------|

| Charge Pump<br>Power Supply                  | Vin                 | 4.75    | 5.0     | 5.5     | V    |                                                       |

| VIN Current<br>(Dynamic) <sup>1</sup>        | IVIND               | —       | 1.7     | 2.75    | mA   | SPI mode, All CH<br>switching at 100Hz                |

| VIN Quiescent<br>Current                     | Ivinq               | —       | 1.65    | 2.25    | mA   | Charge Pump On, All I/O and Channels Static           |

| Low Voltage<br>Logic Supply                  | V <sub>DD</sub>     | 3.0     | 3.3     | 3.6     | V    |                                                       |

| VDD UVLO<br>Rising Threshold                 | UVLORISE            | 2.77    | _       | 2.95    | V    |                                                       |

| VDD UVLO<br>Falling Threshold                | UVLOFALL            | 2.72    | —       | 2.90    | V    |                                                       |

| Low Voltage<br>Digital Current <sup>1</sup>  | Idd                 | —       | 520     | 700     | μA   | SPI mode, All CH<br>Switching at 100Hz                |

| Low Voltage<br>Digital Quiescent<br>Current  | IDDQ                | —       | 480     | 550     | μA   | Charge Pump On,<br>All I/O & Channels Static          |

| Low Voltage<br>Digital Sleep<br>Mode Current | IDDSLEEP            | —       | <1      | 10      | μA   | Charge Pump Off, SPI<br>and Inputs in Static<br>State |

| Logic Reference<br>Level                     | Vdd_10              | 1.71    | —       | 5.25    | V    |                                                       |

| I/O Logic Supply<br>Current                  | I <sub>DD_IOQ</sub> | —       | <10     | 50      | uA   | All Channels Switching at 100Hz                       |

| Notes:                                       |                     |         |         |         |      |                                                       |

#### **Table 7. Power Supply Specifications**

1. Specification is obtained by characterization.

|                                                                                     |                   |                          |         | P                                   |      |                                                                                             |

|-------------------------------------------------------------------------------------|-------------------|--------------------------|---------|-------------------------------------|------|---------------------------------------------------------------------------------------------|

| Parameter                                                                           | Symbol            | Minimum                  | Typical | Maximum                             | Unit | Conditions                                                                                  |

| Logic I/O Level High                                                                | I/O <sub>VH</sub> | 0.7 x V <sub>DD_IO</sub> | _       | V <sub>DD_IO</sub>                  | V    |                                                                                             |

| Logic I/O Level Low                                                                 | I/O <sub>VL</sub> | 0                        | —       | $0.3 \text{ x } V_{\text{DD}_{IO}}$ | V    |                                                                                             |

| Logic I/O Hysteresis<br>(SCK only) <sup>1</sup>                                     | I/О∨н             | _                        | 0.25    | _                                   | V    |                                                                                             |

| Digital Input<br>Capacitance                                                        | CIN               | —                        | 2       | 5                                   | pF   |                                                                                             |

| SDO Load<br>Capacitance <sup>2 3</sup>                                              | Csdo              | —                        | —       | 10                                  | pF   |                                                                                             |

| SDO Source<br>Current @ VDD_IO <sup>1</sup> :                                       | ISDOH             |                          |         |                                     |      | VOUT = 0.8 x<br>VDD_IO                                                                      |

| 5 V                                                                                 |                   | 180                      | 290     | _                                   | mA   |                                                                                             |

| 3.3V<br>1.8V                                                                        |                   | 75                       | 140     | —                                   | mA   |                                                                                             |

| 1.0 V                                                                               |                   | 20                       | 35      | —                                   | mA   |                                                                                             |

| SDO Sink Current @ VDD_IO <sup>1</sup> :                                            |                   |                          |         |                                     |      | VOUT = 0.2 x<br>VDD_IO                                                                      |

| 5.0 V                                                                               |                   | 140                      | 260     | —                                   | mA   |                                                                                             |

| 3.3 V<br>1.8 V                                                                      |                   | 65                       | 140     | —                                   | mA   |                                                                                             |

| 1.0 V                                                                               |                   | 20                       | 40      | —                                   | mA   |                                                                                             |

| Pull down resistor<br>at SDI, SCK, SSB,<br>CP_EN, FLIP_BIT,<br>and FLT_MODE<br>pins | Rpd               | 120                      | 200     | 280                                 | kΩ   | SSB pull down<br>is only in<br>GPIO mode                                                    |

| CP_EN pin toggle<br>low time                                                        | TTOGGLE           | 500                      |         | _                                   | ns   | Minimum time<br>CP_EN has to<br>be held low to<br>restart the IC<br>from fault<br>condition |

| FLTB pin max sink current <sup>1</sup>                                              |                   | 65                       | 140     | —                                   | mA   | FLTB = GND<br>VDD_IO=3.3V                                                                   |

| Notes:                                                                              |                   |                          |         |                                     |      |                                                                                             |

## Table 8. Digital Interface AC and DC Specifications

Notes:

1. Specification is obtained by characterization.

2. Specification is for design guidance only.

3. SDO load capacitance = input capacitance of SDI pin + trace capacitance from SDO to SDI

|                                                                | •               |             | 0.1     |         |      |            |

|----------------------------------------------------------------|-----------------|-------------|---------|---------|------|------------|

| Parameter                                                      | Symbol          | Minimum     | Typical | Maximum | Unit | Conditions |

| SPI Clock<br>Frequency                                         | SCK             | —           | —       | 33      | MHz  |            |

| SDI Valid to SCK<br>Setup Time <sup>1</sup>                    | tsu             | 2           | —       | —       | ns   |            |

| SDI Valid to SCK<br>Hold Time <sup>1</sup>                     | tнd             | 5           | —       | —       | ns   |            |

| SCK High Time <sup>1</sup>                                     | tнı             | 15.5        | —       | —       | ns   |            |

| SCK Low Time <sup>1</sup>                                      | t <sub>LO</sub> | 15.5        | _       | _       | ns   |            |

| SSB Pulse Width <sup>1</sup>                                   | tcsн            | 15          | —       | —       | ns   |            |

| LSB SCK to SSB<br>High <sup>1</sup>                            | tcshld          | 15          | —       | _       | ns   |            |

| SSB Low to SCK<br>High <sup>1</sup>                            | tcssu           | 15          | —       | —       | ns   |            |

| SDO Propagation<br>Delay from SCK<br>Falling Edge <sup>1</sup> | tsdoh           | 10          | _       |         | ns   |            |

| SDO Output Valid<br>after SSB Low <sup>1</sup>                 | tcsdo           | 20          | —       | —       | ns   |            |

| SSB Inactive to<br>SDO High<br>Impedance <sup>1</sup>          | tsdoz           | _           | _       | 10      | ns   |            |

| Notes:                                                         | ained by chara  | cterization |         |         |      |            |

## **Table 9. Digital Interface Timing Specifications**

1. Specification is obtained by characterization.

#### Table 10. Charge Pump and Driver Specifications

| Parameter                       | Symbol          | Minimum | Typical | Maximum | Unit | Conditions                                                                                     |

|---------------------------------|-----------------|---------|---------|---------|------|------------------------------------------------------------------------------------------------|

| Power-On-<br>Reset <sup>1</sup> | POR             |         | 1.25    | 2.5     | ms   | Time for logic input signals<br>to be considered valid<br>after application of VIN<br>and VDD. |

| Start-Up Time                   | T <sub>ST</sub> | —       | 20      | 33      | ms   | CP_EN=1 (CPEN bit=1) to<br>VPP rises to 90% of set<br>value                                    |

| Notes:                          |                 |         |         |         |      |                                                                                                |

1. Specification is for design guidance only.

11 © 2024 Menlo Microsystems, Inc. All Rights Reserved October 29, 2024 <u>www.MenloMicro.com</u>

#### **Hot Switch Restrictions**

The MM5620 is not intended for hot switching applications and care should be taken to insure that switching occurs at less than 0.5 V. Further, the voltage at the switch terminals must be within +/-0.5 V relative to signal ground.

## **Floating Node Restrictions**

RF pins must not be allowed to electrically float during switch operation and therefore require some form of DC path to ground to prevent charge accumulation. The MM5620 uses the superport configuration for improved high frequency performance. See Menlo Micro application note <u>Avoiding Floating Nodes</u> for a detailed explanation of the hazard conditions to avoid and recommended solutions.

#### **MM5620** HS2\_A HS1\_A Т Т C1 HVB HVB ┥┟ T HVD MS2\_A MS1\_A T HVA т ٦ HVD 220nF HVA LS2 A LS1\_A T. T HVC HVC HS2\_B HS1\_B T т C2 HVB HVB MS1\_B MS2\_B HVD T HVA Т T HVD HVÅ 220nF LS1\_B ( LS2\_B Ť T ніс HVC H HVB Į ž GND Ō **High-Voltage** +3.3V VDD AGND Driver CPGND 0 Charge +90V VPP VIN Pump 0.1 uF 4.7 nF +1.8V to +5V DGND VDD\_IO D **≷**4.99 kΩ **Digital Core** PULL\_UP MODE SCK/CTL1 FLIP\_BIT MOSI/CTL2 FLTB MISO/CTL3 FLT\_MODE CP\_EN SSB/CTL4

Note: C1 and C2 are 220 nF internal capacitors.

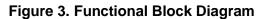

# **Package / Pinout Information**

Figure 4. Package Pinout (Top View/As Mounted)

See <u>Table 11</u> for detailed pin descriptions.

| Pin Name  | Pin # | Description                                                                                                                                                        |

|-----------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| HS1A      | E15   | Port 1A of the high-speed signal path. Can be used as an input or an output.                                                                                       |

| HS1B      | H15   | Port 1B of the high-speed signal path. Can be used as an input or an output.                                                                                       |

| MS1A      | B15   | Port 1A of the medium-speed signal path.<br>Can be used as an input or an output.                                                                                  |

| MS1B      | L15   | Port 1B of the medium-speed signal path.<br>Can be used as an input or an output.                                                                                  |

| LS1A      | B12   | Port 1A of the low-speed signal path. Can be used as an input or an output.                                                                                        |

| LS1B      | B10   | Port 1B of the low-speed signal path. Can be used as an input or an output.                                                                                        |

| HS2A      | E2    | Port 2A of the high-speed signal path. Can be used as an input or an output.                                                                                       |

| HS2B      | H2    | Port 2B of the high-speed signal path. Can be used as an input or an output.                                                                                       |

| MS2A      | B2    | Port 2A of the medium-speed signal path.<br>Can be used as an input or an output.                                                                                  |

| MS2B      | L2    | Port 2B of the medium-speed signal path.<br>Can be used as an input or an output.                                                                                  |

| LS2A      | B5    | Port 2A of the low-speed signal path. Can be used as an input or an output.                                                                                        |

| LS2B      | B7    | Port 2B of the low-speed signal path. Can be used as an input or an output.                                                                                        |

| SCK/CTL1  | T10   | Clock input in SPI mode; RF channel control in GPIO mode. Has an internal pull-down resistor.                                                                      |

| MOSI/CTL2 | Т9    | SPI data input (SDI) in SPI mode; RF channel control in GPIO mode. Has an internal pull-down resistor.                                                             |

| MISO/CTL3 | Τ8    | SPI data output (SDO) in SPI mode; RF channel control in GPIO mode. Has an internal pull-down resistor.                                                            |

| SSB/CTL4  | Τ7    | Chip select in SPI mode; RF channel control<br>in GPIO mode. Has an internal pull-up<br>resistor in SPI mode, and an internal pull-<br>down resistor in GPIO mode. |

|           |       |                                                                                                                                                                    |

#### Table 11. Detailed Pin Description

15 © 2024 Menlo Microsystems, Inc. All Rights Reserved October 29, 2024

| Pin Name | Pin #   | Description                                                                                                                                                                                                        |

|----------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| FLT_MODE | T14     | Fault Mode select in GPIO mode. Fault Mode is disabled if high. Has a built-in pull-down resistor. Pin is ignored in SPI mode.                                                                                     |

| FLTB     | T16     | Fault indicator in GPIO and SPI modes.<br>Open drain output to allow "Wire-OR" of<br>multiple ICs. Goes low when a fault is<br>detected. Can be left open if not used. Pull-<br>up voltage must be ≤ VDD_IO.       |

| FLIP_BIT | R16     | This pin has an internal pull-down resistor. In SPI mode, this pin should be tied to VDD_IO. In GPIO mode FLIP_BIT should be tied to GND. Refer to <u>Table 12</u> for more information.                           |

| MODE     | Т3      | Logic level input to switch inputs between<br>SPI and GPIO modes. MODE = 0 is SPI<br>mode. MODE=1 is GPIO mode.                                                                                                    |

| CP_EN    | Τ6      | Charge pump enable pin in GPIO mode.<br>Pull-up to VDD_IO to enable the charge<br>pump. Has a built-in pull-down resistor. Pin is<br>ignored in SPI mode.                                                          |

| VDD      | R4, T5  | 3.3 V nominal input to digital logic and internal level translators. Bypass with a low ESR 1 $\mu$ F ceramic capacitor.                                                                                            |

| VDD_IO   | Τ4      | For 3.3 V nominal digital I/O levels, connect<br>to VDD. For alternate I/O levels,<br>connect to a separate supply (+1.8V to<br>+5.0V). Bypass with a low ESR 1 $\mu$ F ceramic<br>capacitor if separate from VDD. |

| PULL_UP  | T15     | Connect this pin directly to the FLTB. Has a built-in 4.99 k $\Omega$ resistor to VDD_IO.                                                                                                                          |

| DGND     | R3, T11 | Digital ground, should be connected to PCB ground. The R3 pin has an internal pull-down resistor, it can be left floating.                                                                                         |

| VIN      | P16     | Connect to 5 V power supply. Bypass with a low ESR 1 $\mu$ F ceramic capacitor.                                                                                                                                    |

| CPGND    | T13     | Charge pump ground, should be connected to PCB ground.                                                                                                                                                             |

| VPP      | T1      | High-voltage (90V) charge pump output.<br>Leave this pin unconnected.                                                                                                                                              |

| AGND     | T12     | Analog ground, should be connected to PCB ground.                                                                                                                                                                  |

| Pin Name | Pin #                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Description                                                                                     |

|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|

| GND      | A1,C1,D1,F1,G1,J1,K1,M1,N1,<br>A2,C2,D2,F2,G2,J2,K2,M2,N2,<br>A3,B3,C3,D3,E3,F3,G3,H3,J3,K3,L3,M3,N3,<br>A4,B4,C4,D4,E4,F4,G4,H4,J4,K4,L4,M4,N4,<br>C5,D5,E5,F5,G5,H5,J5,K5,L5,M5,N5,<br>A6,B6,C6,D6,E6,F6,G6,H6,J6,K6,L6,M6,N6,<br>C7,D7,E7,F7,G7,H7,J7,K7,L7,M7,N7,<br>A8,B8,C8,D8,E8,F8,G8,H8,J8,K8,L8,M8,N8,<br>P8,R8,<br>A9,B9,C9,D9,E9,F9,G9,H9,J9,K9,L9,M9,N9,<br>P9,R9,<br>C10,D10,E10,F10,G10,H10,J10,K10,L10,<br>M10,N10,<br>A11,B11,C11,D11,E11,F11,G11,H11,J11,<br>K11,L11,M11,N11,<br>C12,D12,E12,F12,G12,H12,J12,K12,L12,<br>M12,N12,<br>A13,B13,C13,D13,E13,F13,G13,H13,J13,<br>K13,L13,M13,N13,<br>A14,B14,C14,D14,E14,F14,G14,H14,J14,<br>K14,L14,M14,N14,<br>A15,C15,D15,F15,G15,J15,K15,M15,N15,<br>A16,C16,D16,F16,G16,J16,K16,M16,N16 | Connect to common ground. These pins are<br>internally connected to the RF ground<br>reference. |

# **RF Performance**

Typical device performance, measured on MM5620 EVK at room temperature.

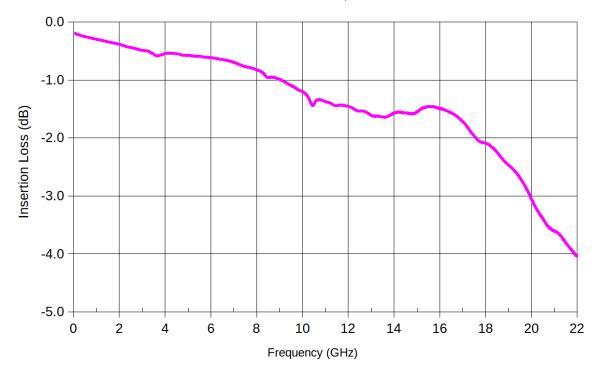

## Insertion Loss / SDD21

MM5620 HS1 TO HS2, De-embedded

Figure 5. Insertion Loss/SDD21

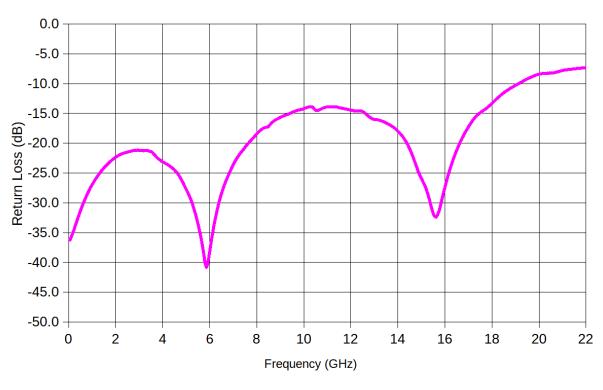

# Return Loss / SDD11 MM5620 HS1 TO HS2, De-embedded

Figure 6. Return Loss/SDD11

The return loss performance from 8 to 14 GHz can be improved by optimizing the PCB launch to the MM5620 device. Please contact your local Menlo Micro sales support for further information.

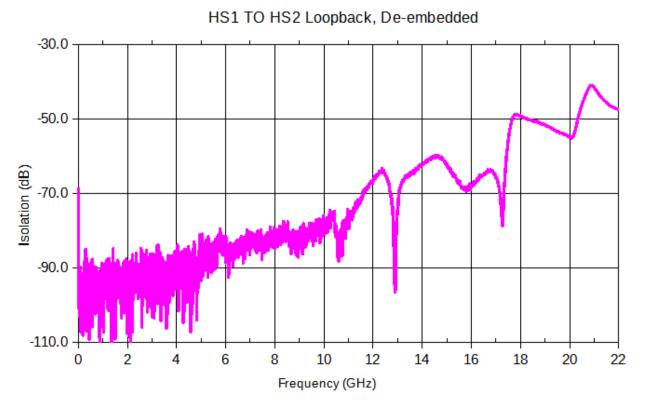

# Isolation / SDD21

Figure 7. Isolation/SDD21

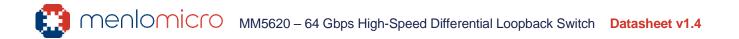

# Programming

## **Communication Interface**

The MM5620 has two modes of operation; **SPI (serial)** and **GPIO (Parallel)**, selected by the **MODE** input pin.

All the SPI pins (except SSB pin), the FLIP\_BIT, the FLT\_MODE pin, and the CP\_EN pin have an internal pull-down resistor to ensure that no digital input pins are left floating.

The SSB pin has a pull-up current source in SPI mode. This ensures that the IC defaults to a disabled state in SPI mode. In GPIO mode, this pin is CTL4. In this case, the SSB pin has a pull-down resistor. This ensures that the input is low by default in GPIO mode.

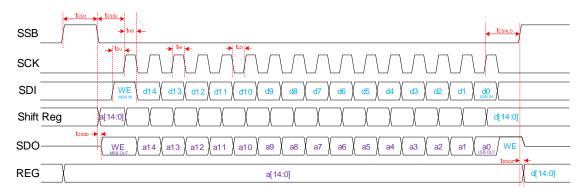

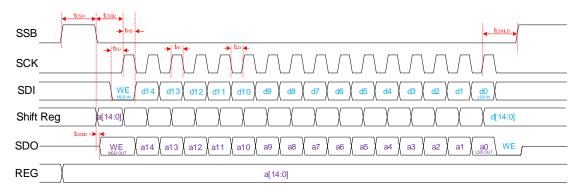

Figure 8. SPI Timing Diagram

## **Serial Communication**

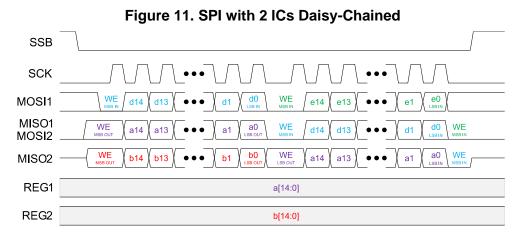

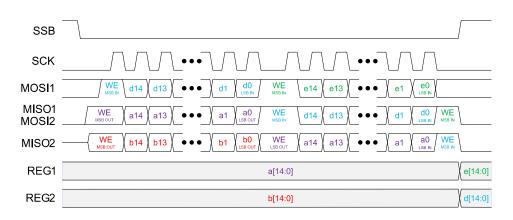

MODE = 0, activates the 16-Bit Serial Peripheral Interface (SPI) module for operation. Multiple devices can be daisy-chained to drive multiple ICs using one SPI bus (see <u>Daisy Chain Operation</u>, <u>Figure 11</u>, <u>Figure 12</u>, and <u>Figure 13</u>). The SPI works at any frequency up to a maximum of 33 MHz and may operate at significantly lower frequencies if the logic signals adhere to the data setup and hold requirements.

#### **SPI Interface Mode**

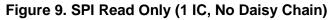

SPI timing diagrams are provided in Figure 8 through Figure 13 In SPI mode, data transmission starts when SSB goes Low, causing the Target to output the Most Significant Bit (MSB) of data to the SDO (MISO) pin. Data transfer from Host to Target takes place during the rising edge of the clock (SCK), which is idle when SSB is High. This mode of operation requires data for Host and Target to be present on SDI (MOSI) before the rising edge of the clock (defining SDI to SCK setup time). Data is pushed out of the SDO (MISO) pin during the falling edge of the clock. After the first 16-bit transaction, Host writes the latest data (DN) to

Target, while Target passes its previous (DN-1) stored data to the Host. Data is latched into the internal registers at the rising edge of SSB, if WR\_EN = 1.

#### **SPI** Data Format

SPI data is sent in a 16-bit format. The first MSB bit (WE), if high, enables the Write mode. The following 7 MSB bits hold the Control and Fault Status bits. The 8 LSB bits hold the Switch State bits.

Figure 10. SPI Read & Write (1 IC, No Daisy Chain)

#### **SPI Control Registers**

The SPI interface provides access to two 8-bit Internal Registers: Register STATE and Register CONTROL that are Read/Write registers. Register data is read by toggling SSB low and monitoring the data at the SDO pin while clocking the SCK pin. Register STATE holds the state of the 4 internal high-voltage outputs and is updated when SSB goes from LOW to HIGH, if the Write Enable bit is high.

Register CONTROL holds four control bits (CPEN, VPPCOMP, FLT\_MODE, and SLEEP), and the fault status bit (FSTAT). The MSB bit enables the Write mode if high. In SPI mode, the CP\_EN and FLT\_MODE pins are ignored. Settings in the CONTROL register are used instead.

**Note:** The first row of the register tables below shows the read/write type, and default state. At power-on-reset (POR), all bits in both registers are set to LOW internally.

#### **State Register**

| R/W - 0 | R/W – 0 |

|---------|---------|---------|---------|---------|---------|---------|---------|

| 0       | 0       | 0       | 0       | HVD     | HVC     | HVB     | HVA     |

| bit7    |         |         |         |         |         |         | bit 0   |

bit 7: Low

Set this bit low.

#### bit 6: **Low**

Set this bit low.

#### bit 5: **Low**

Set this bit low.

#### bit 4: **Low**

Set this bit low.

bit 3: HVD

- 1 = HVD Output is Enabled (High)

- 0 = HVD Output is Disabled (Low)

- bit 2: HVC

- 1 = HVC Output is Enabled (High)

- 0 = HVC Output is Disabled (Low)

```

bit 1: HVB

```

- 1 = HVB Output is Enabled (High)

- 0 = HVB Output is Disabled (Low)

- bit 0: HVA

- 1 = HVA Output is Enabled (High)

- 0 = HVA Output is Disabled (Low)

#### **Control Register**

| R/W - 0 | R/W – 0 |

|---------|---------|---------|---------|---------|---------|---------|---------|

| WR_EN   | FSTAT   | SLEEP   | FLTMODE | VPPCOMP | Х       | CPEN    | Х       |

| bit7    |         |         |         |         |         |         | bit 0   |

bit 7: WR\_EN

1 = Enable write mode

0 = Disable Write mode (read only)

bit 6: FSTAT (see Note 1 below)

1 = VPP OR VDD Fault status = faulted

0 = VPP OR VDD Fault status = NOT faulted

#### bit 5: SLEEP

1 = SLEEP mode active (all analog circuits disabled)

- 0 = SLEEP mode inactive (all analog circuits enabled)

- bit 4: FLTMODE

1 = Fault Mode Disabled (shutdown Disabled)

0 = Fault Mode Enabled (shutdown Enabled)

#### bit 3: VPPCOMP

1 = VPP under-voltage comparator is disabled.

0 = VPP under-voltage comparator is active.

bit 2: Do Not Care

This bit can be set to either state without effecting performance.

#### bit 1: CPEN

1 = Charge Pump is enabled

0 = Charge Pump is disabled

#### bit 0: Do Not Care

This bit can be set to either state without effecting performance.

#### Notes:

1. After this bit is set high, it must be written to 0 to clear the fault. If fault mode is enabled, CPEN must be toggled to restart the charge pump. See Fault Conditions for more information.

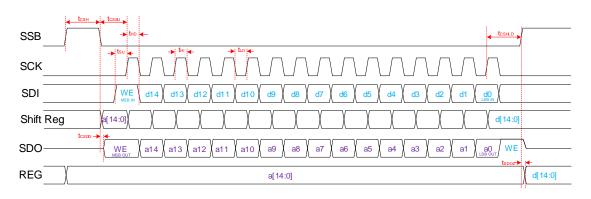

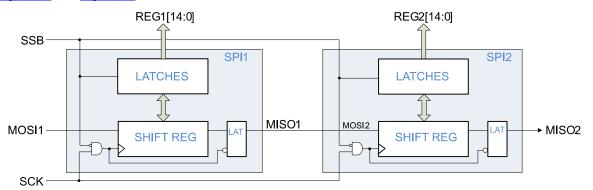

## **Daisy Chain Operation**

Daisy chaining the ICs is permitted and involves connecting the MISO of one chip to the MOSI of the next chip in the chain, as shown in <u>Figure 11</u>. SPI timing diagrams with daisy-chained devices are provided in <u>Figure 12</u> and <u>Figure 13</u>.

Figure 12. SPI Read Only (2 ICs Daisy-chained)

## **GPIO Communication**

MODE = 1 and FLIP\_BIT = 0 activates the GPIO (General Purpose Input Output or Parallel) Communication Mode. In this mode of operation, the SPI Interface pins act as parallel inputs, as described in <u>Table 11</u>. <u>Detailed Pin Description</u>. Valid switch states are listed here.

|       |          | Inpu | t Signal | s    |      |     | HVG | JUT |     |                         |

|-------|----------|------|----------|------|------|-----|-----|-----|-----|-------------------------|

| Count | FLIP_BIT | CTL4 | CTL3     | CTL2 | CTL1 | D   | с   | в   | А   | Switch State            |

| 0     | 0        | 0    | 0        | 0    | 0    | OFF | OFF | OFF | OFF | ALL OFF (OPEN)          |

| 1     | 0        | 0    | 0        | 0    | 1    | OFF | OFF | OFF | ON  |                         |

| 2     | 0        | 0    | 0        | 1    | 0    | OFF | OFF | ON  | OFF |                         |

| 3     | 0        | 0    | 0        | 1    | 1    | OFF | OFF | ON  | ON  | HS1 – HS2               |

| 4     | 0        | 0    | 1        | 0    | 0    | OFF | ON  | OFF | OFF |                         |

| 5     | 0        | 0    | 1        | 0    | 1    | OFF | ON  | OFF | ON  | LS1 – LS2               |

| 6     | 0        | 0    | 1        | 1    | 0    | OFF | ON  | ON  | OFF | HS1 – LS1 and HS2 – LS2 |

| 7     | 0        | 0    | 1        | 1    | 1    | OFF | ON  | ON  | ON  |                         |

| 8     | 0        | 1    | 0        | 0    | 0    | ON  | OFF | OFF | OFF |                         |

| 9     | 0        | 1    | 0        | 0    | 1    | ON  | OFF | OFF | ON  | MS1 – MS2               |

| 10    | 0        | 1    | 0        | 1    | 0    | ON  | OFF | ON  | OFF | HS1 – MS1 and HS2 – MS2 |

| 11    | 0        | 1    | 0        | 1    | 1    | ON  | OFF | ON  | ON  |                         |

| 12    | 0        | 1    | 1        | 0    | 0    | ON  | ON  | OFF | OFF | MS1 – LS1 and MS2 – LS2 |

| 13    | 0        | 1    | 1        | 0    | 1    | ON  | ON  | OFF | ON  |                         |

| 14    | 0        | 1    | 1        | 1    | 0    | ON  | ON  | ON  | OFF |                         |

| 15    | 0        | 1    | 1        | 1    | 1    | ON  | ON  | ON  | ON  | ALL ON (CLOSED)         |

Table 12. State Table in GPIO Mode

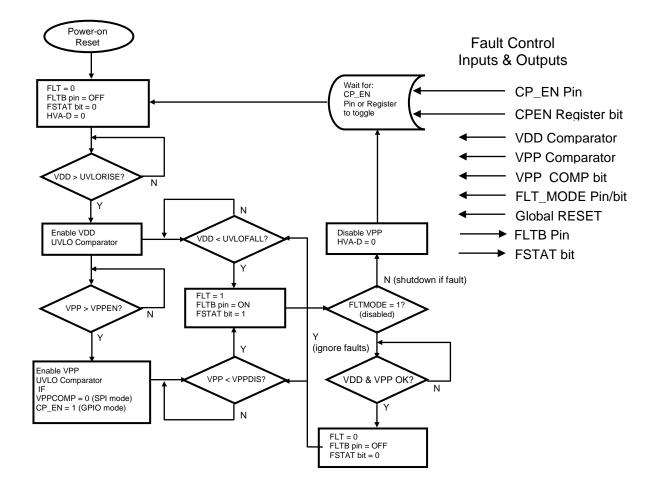

## **Fault Conditions**

There are two comparators that can signal a fault condition - VDD under voltage fault and VPP under voltage fault. Faults are reported differently depending on the mode of communication - SPI or GPIO.

**Note:** The VPP under voltage comparator can be disabled. In SPI mode, it is disabled when the VPPCOMP bit in the CONTROL register is high. In GPIO mode, the comparator is disabled when CP\_EN pin is set low.

The outputs of the VDD and VPP fault comparators are logically OR'ed. The output of the OR gate controls the FLTB pin. FLTB is an open-drain output and is ON (low impedance) if either fault is detected. In SPI mode, bit 6 of the CONTROL register provides VDD and VPP fault status.

At start-up, the FLTB pin is held OFF (high impedance). It is allowed to change state only after each voltage goes past its Enable threshold (VDD goes higher than UVLO<sub>RISE</sub> and VPP goes higher than V<sub>EN</sub>). This prevents a race condition at startup.

Once VDD and VPP go above their thresholds, the comparators monitoring VDD and VPP actively monitor for faults. If VDD goes below  $UVLO_{FALL}$  or VPP goes below  $VPP_{DIS}$ , a fault condition is signaled by setting the FLTB pin low and the Fault Status bit high (bit 6 in the CONTROL register). The FLTB pin returns to an open state when the fault condition is cleared and the FSTAT bit remains latched high until it is cleared via a SPI write. If Fault Mode is enabled (in GPIO mode, FLT\_MODE pin = 0, in SPI mode, FLT\_MODE bit = 0), the internal high-voltage outputs are all set low (all switches open) and the charge pump is turned off. The user must toggle the CP\_EN pin (GPIO mode) or the CPEN register bit (SPI mode) low and then high to restart the device.

If Fault Mode is disabled (in GPIO mode, FLT\_MODE pin = 1; in SPI mode, FLT\_MODE bit = 1), no action is taken by the IC. The fault condition is reported but does not affect the charge pump operation or switch states.

Figure 14. Flowchart for Fault

#### Notes:

- 1. The un-faulted supply continues to be monitored when a fault occurs. The FLT signal remains faulted until both supplies are above their brownout trip level.

- 2. VDD\_IO is not monitored unless it is connected to VDD.

- 3. VPP is not monitored if: VPPCOMP = 1 in SPI mode OR the CP\_EN pin is low In GPIO mode.

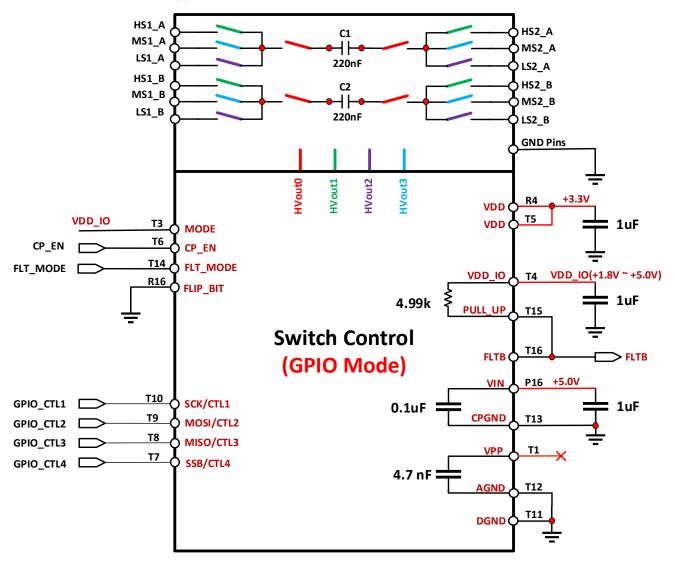

# **Application Circuit Diagram**

Figure 15, Figure 16, and Figure 17 show a few MM5620 application diagrams. For additional applications, refer to the MM5620 Application Notes.

Figure 15. External Circuits for GPIO Mode

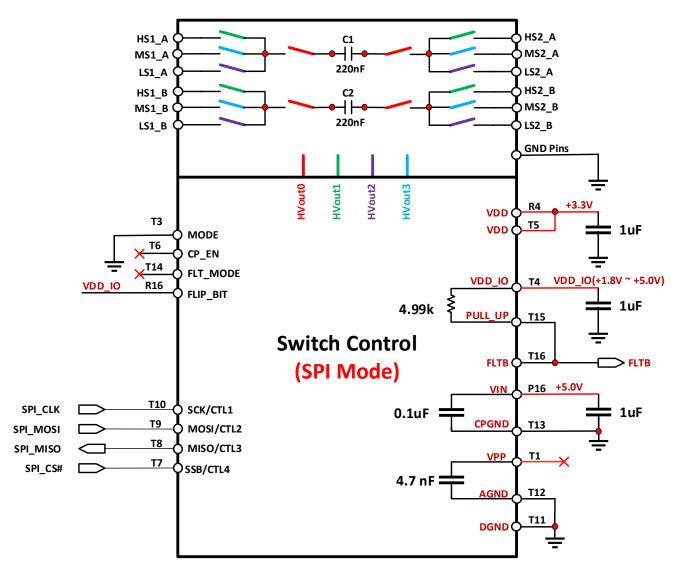

Figure 16. External Circuits for SPI Mode

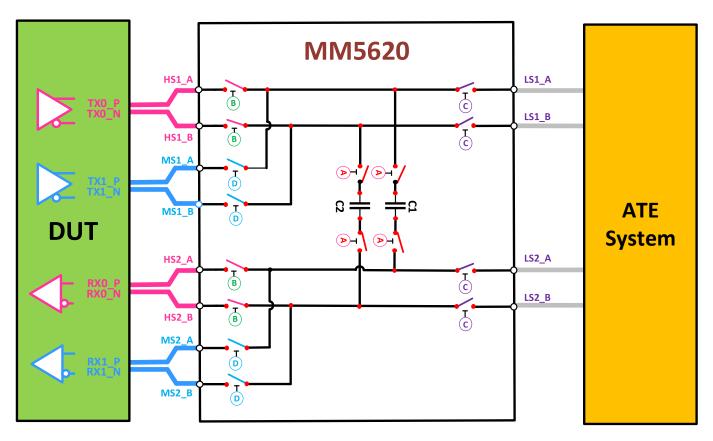

Figure 17. Double-Density HSIO Loopback Mode Test

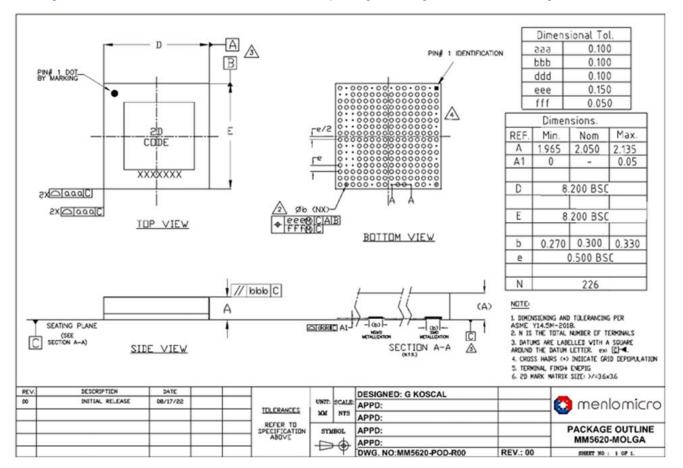

# **Package Drawing**

Figure 18 shows the 8.2 mm x 8.2 mm 226P LGA package drawing. All dimensions are given in millimeters.

Figure 18. Package Drawing

# **MM5620 EVK PCB Layout**

Figure 19 shows the PCB layout based on the MM5620 EVK stack-up.

Figure 19. MM5620 EVK PCB Layout

Please contact your local Menlo Micro sales support for further information.

# **Recommended Solder Reflow Profile**

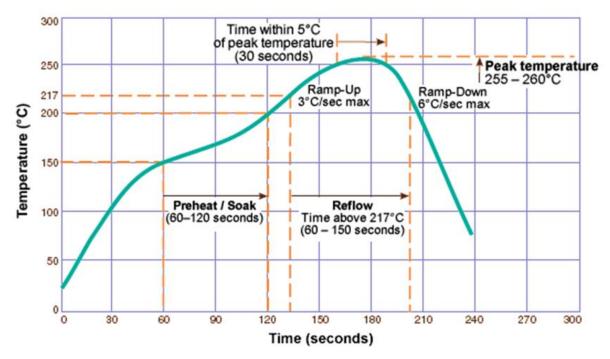

Figure 20. Reflow Profile

Reflow profiles and assembly guidelines are given for RoHS-compliant (lead-free) solder alloy.

Follow Moisture Sensitivity Level (MSL) 3 handling precautions specified in IPC/JEDEC J-STD-020.

# **Storage and Shelf Life**

Under typical industry storage conditions (≤30 °C/60% RH) in Moisture Barrier Bags, the following is recommended:

- Customer Shelf Life: 24 months from customer receipt date.

- Extended Shelf Life: 60 months from customer receipt date if re-bagged every 24 months or less.

# **Package Marking Information**

Dot • = Pin 1 Indicator Line 1 = 2D Bar Code Line 2 = Human-readable product code

Figure 21. Package Marking Drawing

# **Package Options and Ordering Information**

All Menlo Micro solutions are EAR99 compliant.

| Part Number     | Package Description                                                                                               | Temp Range   | Device Marking <sup>1</sup> |

|-----------------|-------------------------------------------------------------------------------------------------------------------|--------------|-----------------------------|

| MM5620-01NDB    | Dual DPDT w/internal charge<br>pump - loopback high-speed<br>64Gbps - 8.2mm x 8.2mm LGA<br>Industrial Temperature | -40C to +85C | CBxxxxx                     |

| MM5620-01NDB-TR | Dual DPDT w/internal charge<br>pump - loopback high-speed<br>64Gbps - 8.2mm x 8.2mm LGA<br>Industrial Temperature | -40C to +85C | CBxxxxx                     |

|                 | Tape and Reel (Qty 250)                                                                                           |              |                             |

| MM5620EVK2A     | High-performance evaluation board<br>pump-loopback, w/Southwest conne<br>8.2mmx8.2mm LGA                          |              |                             |

| MM5620EVK2B     | High-performance evaluation board<br>pump-loopback, w/Southwest conne<br>8.2mm x8.2mm LGA                         |              |                             |

#### Notes:

1. Additional markings may be present, including logo or lot trace code information. This information may be a 2D barcode or other human-readable markings. Note that 'x' is a placeholder for a 5-digit numerical code.

| Legacy Product | New Proc     | duct Name                  |

|----------------|--------------|----------------------------|

| Name           | Bulk         | Tape and Reel <sup>1</sup> |

| MM5620-01      | MM5620-01NDB | MM5620-01NDB-TR            |

1. 250pcs standard tape and reel increment.

# **Important Information**

## **Disclaimer**

The data presented in this document is for informational purposes only and shall in no event be regarded as a guarantee of conditions or characteristics. Any warranty or license for this product shall be specified and governed by the terms of a separate purchase agreement. Menlo Micro does not assume any liability arising out of the application or use of this product; neither does it convey any license under its patent rights, nor the rights of others.

Menlo Micro reserves the right to make changes in these specifications and features shown herein to improve reliability, function, and design; or to discontinue this product at any time without notice or obligation. Contact our product representative for the most current information.

## Warning

This product is not authorized for use:

- In any life support systems.

- Applications for implanting into the human body, without the express written approval from Menlo Micro.

## **Trademark Notices**

All trademarks and product service marks are owned by Menlo Microsystems, Inc.

## **Contact Information**

Please contact Menlo Micro for the latest specifications, additional product information, test and evaluation boards, product samples, worldwide sales and distribution locations:

Internet: <u>www.menlomicro.com</u> E-mail: <u>sales@menlomicro.com</u>

For product technical questions and application information: support@menlomicro.com.